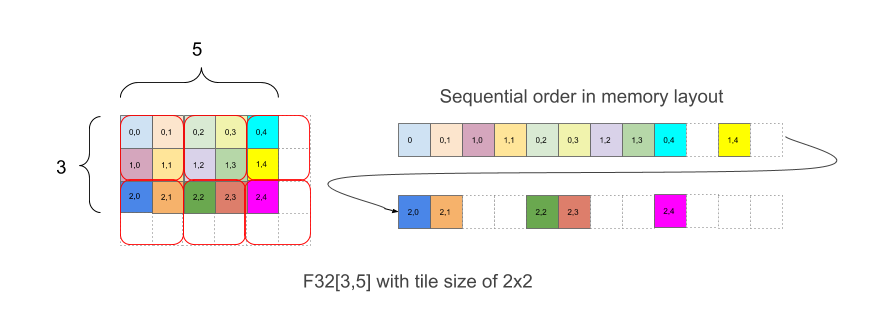

पहली इमेज

पहली इमेज में दिखाया गया है कि कैसे 2x2 टाइल की मदद से, मेमोरी में F32[3,5] ऐरे को रखा जाता है. इस लेआउट में एक आकार F32[3,5]{1,0:T(2,2)} के तौर पर लिखा जाता है, जिसमें 1,0, डाइमेंशन के फ़िज़िकल ऑर्डर (लेआउट में minor_to_major फ़ील्ड) से जुड़ा होता है, जबकि (2,2) कोलन के बाद, 2x2 टाइल से फ़िज़िकल डाइमेंशन को टाइल करने का पता चलता है.

आसानी से, आकार को ढंकने के लिए और हर टाइल के अंदर, एलिमेंट को टाइल के बिना रखा जाता है. जैसा कि ऊपर दिए गए उदाहरण में बताया गया है, जहां उदाहरण के दाएं हिस्से में, मेमोरी में लेआउट दिखता है. इसमें व्हाइट पैडिंग के एलिमेंट शामिल होते हैं जिन्हें 2x2 टाइल को पूरा करने के लिए जोड़ा जाता है, भले ही मूल अरे की सीमाएं समान न हों.

पैडिंग में अतिरिक्त एलिमेंट में कोई खास वैल्यू शामिल करना ज़रूरी नहीं है.

आकार और टाइल के आधार पर टाइलिंग के लिए, लीनियर इंडेक्स फ़ॉर्मूला

टाइलिंग के बिना, d=(dn, dn-1, ... , d1) वाली कलेक्शन में मौजूद एलिमेंट e=(en, en-1, ... , e1) को पोज़िशन पर मेजर से माइनर क्रम में तय किया जाता है:

Linear_index(e, d)

= Linear_index((en, en-1, ... , e1),

(dn, dn-1, ... , d1))

= endn-1...d1 +d n-1...d1 + n-1 ...

इस दस्तावेज़ में नोटेशन की आसानी के लिए, हम मान लेते हैं कि टाइल में मौजूद डाइमेंशन की संख्या, अरे की संख्या के बराबर है. एक्सएलए में टाइल लागू करते समय, इसे सामान्य तौर पर कम डाइमेंशन वाली टाइलिंग के लिए तैयार किया जाता है. ऐसा सबसे पहले मुख्य डाइमेंशन में कोई बदलाव करके नहीं किया जाता. साथ ही, सबसे छोटे डाइमेंशन पर टाइलिंग लागू की जाती है, ताकि बताई गई टाइल, टाइल किए जा रहे आकार के फ़िज़िकल डाइमेंशन के सफ़िक्स का उल्लेख करे.

जब (tn, tn-1, ... , t1) साइज़ की टाइल का इस्तेमाल किया जाता है, तब इंडेक्स (en, en-1, ... , e1) वाली कलेक्शन में मौजूद एक एलिमेंट को फ़ाइनल लेआउट में इस पोज़िशन के लिए मैप किया जाता है:

linear_index_with_with_title(e, d, t)

=linear_index((⌊e/t⌋, t)) (ऐरिथमेटिक, एलिमेंटवाइस, (a,b)...nnzn ∁ ∋/∋nat, ∋ ∋/∋∋/∇∋/∋∈t1, ∈∋/∋∈∋/∈∋t ∋t, t)

=linear_index((⌊e/t⌋, t)) (ऐरिथमेटिक तरह एलिमेंटवाइस, (a,b)...nn

लेआउट के दो हिस्सों को इस तरह समझा जा सकता है: (⌊en/tn⌋, ... , ⌊e1/t1⌋), जो साइज़ की कैटगरी वाली टाइल में मौजूद टाइल इंडेक्स की तरह हैं (⌈dn/tn उनकी ... , /∉tnn ... , /∉tng के अंदर ⌊en/tn⌋, ... , ⌊e1/t1⌋), सीइल फ़ंक्शन, ⌈di/ti⌉ में दिखता है, क्योंकि अगर टाइल बड़ी रेंज की सीमाओं को पार करती हैं, तो पैडिंग (जगह) को पहली इमेज की तरह डाला जाता है. टाइलों के अंदर की टाइल और एलिमेंट, दोनों को टाइल के बिना, बार-बार लगाया जाता है.

इमेज 1 के उदाहरण के लिए, (1,1,0,1) के कंबाइंड कोऑर्डिनेट वेक्टर के लिए, एलिमेंट (2,3) में टाइल इंडेक्स (1,1) और इन-टाइल इंडेक्स (0,1) है. टाइल इंडेक्स में (2,3,2,2) के कंबाइंड वेक्टर के लिए बाउंड (2,3) और टाइल (2,2) है. लॉजिकल आकार में इंडेक्स (2,3) वाले एलिमेंट के लिए टाइल वाला लीनियर इंडेक्स

जुलते

पैड के आकार को बदलने के रूप में टाइलिंग

टाइलिंग-आधारित लेआउट इस तरह काम करता है:

डाइमेंशन की कैटगरी (dn, dn-1, ... , d1) (d1

सबसे छोटा डाइमेंशन है) चुनें. जब टाइल का साइज़ (tn, tn-1, ... , t1) (t1 सबसे छोटा डाइमेंशन होता है) की टाइल के साथ बनाया जाता है, तो उस टाइल को पैड के आकार में ट्रांसपोज़ करके इस तरह समझा जा सकता है.

- ऐरे को (⌈dn/tn⌉換n, ... , ⌈d1/t1⌉secondaryt1) में जोड़ा जाता है.

- हर डाइमेंशन i को (⌈di/ti⌉,

ti) में बांटा जाता है. इसका मतलब है कि ऐरे को

(⌈dn/tn, tn, ... , ⌈d1/t1, t1) में बदल दिया जाता है.

इस आकार में अपने-आप कोई फ़िज़िकल लेआउट में बदलाव नहीं होता, इसलिए यह आकार बिटकास्ट होता है. अगर किसी टाइल के बारे में साफ़ तौर पर नहीं सोचा जा रहा है, तो यह बदलाव किसी भी आकार को पैड किए गए आकार के बराबर एलिमेंट तक के आकार में दिखा सकता है - यहां उदाहरण के तौर पर बताया गया है कि टाइल को इस तरह कैसे दिखाया जाए. - ट्रांसपोज़ करते समय, tn, ... , t1 को सबसे माइनर डाइमेंशन पर ले जाया जाता है. साथ ही, यह एक क्रम में रखा जाता है, ताकि डाइमेंशन का क्रम सबसे ज़्यादा माइनर डाइमेंशन से

हो जाए. (dn/tn⌉, ... , ⌈d1/t1⌈, t, t).n

फ़ाइनल आकार में प्रीफ़िक्स

(⌈dn/tn⌉, ... ,

⌈d1/t1⌉) होता है, जो हर डाइमेंशन में टाइल की संख्या बताता है. कलेक्शन में मौजूद एक एलिमेंट (en, ... , e1) को इस एलिमेंट के साथ फ़ाइनल आकार में मैप किया जाता है:

(⌊en/tn⌋, ... ,

⌊e0/t0⌋, en mod tn, ... ,

e1). यह देखना आसान है कि एलिमेंट का लीनियर इंडेक्स, ऊपर दिए गए फ़ॉर्मूला के हिसाब से काम करता है.

बार-बार टाइल लगाने की सुविधा

XLA की टाइलिंग, बार-बार लागू होने से और ज़्यादा सुविधाजनक हो जाती है.

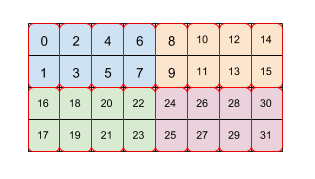

दूसरी इमेज

दूसरी इमेज में दिखाया गया है कि 4x8 साइज़ के अरे को टाइलिंग के दो लेवल (पहले 2x4 फिर 2x1) से कैसे टाइल किया जाता है. हम इस दोहराई गई टाइल को (2,4)(2,1) के तौर पर दिखाते हैं. हर रंग 2x4 टाइल के बारे में बताता है और हर लाल बॉर्डर बॉक्स में 2x1 टाइल होती है. संख्याएं, टाइल वाले फ़ॉर्मैट में उस एलिमेंट की मेमोरी में लीनियर इंडेक्स को दिखाती हैं. यह फ़ॉर्मैट, TPU पर BF16 के लिए इस्तेमाल किए गए फ़ॉर्मैट से मेल खाता है. हालांकि, इसकी शुरुआती टाइल (8,128)(2,1) बड़ी है. इसमें 2x1 की दूसरी टाइलिंग का मकसद, दो 16-बिट वैल्यू को एक साथ इकट्ठा करके, 32-बिट की वैल्यू को इस तरह इकट्ठा करना है कि यह TPU के आर्किटेक्चर के साथ मेल खाए.

ध्यान दें कि दूसरी या बाद की टाइल, टाइल के अंदर के माइनर डाइमेंशन के बारे में बता सकती है. यह टाइल में डेटा को सिर्फ़ फिर से व्यवस्थित करता है, जैसा कि इस उदाहरण में (8,128)(2,1) के साथ किया गया है. हालांकि, यह पहले की टाइल के मुख्य क्रॉस-टाइल डाइमेंशन भी बता सकता है.

टाइल का इस्तेमाल करके डाइमेंशन जोड़ना

XLA की टाइलिंग, डाइमेंशन को मिलाने में भी मदद करती है. उदाहरण के लिए, यह F32[2,7,8,11,10]{4,3,2,1,0} में मौजूद डाइमेंशन को F32[112,110]{1,0} में मिला सकता है. इसके बाद, उन्हें (2,3) टाइल किया जा सकता है. इस तरह की टाइल का इस्तेमाल किया जाता है (∗,∗,2,∗,3). यहां टाइल में तारे का निशान लगाने का मतलब है कि उस डाइमेंशन को छोटे डाइमेंशन के साथ जोड़ना. एक से ज़्यादा सन्निकट डाइमेंशन को एक डाइमेंशन में शामिल किया जा सकता है. टाइल के उस डाइमेंशन में शामिल डाइमेंशन को -1 की टाइल वैल्यू से दिखाया जाता है, जो किसी टाइल में डाइमेंशन साइज़ के तौर पर मान्य नहीं है.

ज़्यादा सटीक तौर पर, अगर टाइल में तारे के निशान के ज़रिए आकार का डाइमेंशन i हटा दिया जाता है, तो टाइलिंग की पहले की परिभाषा लागू होने से पहले, उस डाइमेंशन को टाइल किए जा रहे आकार और टाइल वेक्टर, दोनों से हटा दिया जाता है और आकार के डाइमेंशन i-1 की अरे की सीमा di-1 से didi-1 तक बढ़ जाती है. यह चरण टाइल वेक्टर में हर तारे के निशान के लिए दोहराया जाता है.